Doc.Nr. 8260800.06

#

# Product Family Specification

SCP1000 Series Absolute pressure sensor

SCP1000-D01 SCP1000-D11

Note: Reader is advised to notice that this Product Family Specification applies to SCP1000 version which is equipped with the first release of signal conditioning circuitry. It can be recognized from the P01 or P03 marking on the top of the component (see image). If you are using SCP1000 version marked with either D01 or D11, please use Product Family Specification rev. 0.07. Differences between the first and second release of SCP1000 signal conditioning circuitry versions are described in Technical Note 59 (SCP1000 ASIC Update).

# **Table of Contents**

| 1 | Gei               | neral Description                                        | .5 |

|---|-------------------|----------------------------------------------------------|----|

|   | 1.1               | Introduction                                             | .5 |

|   | 1.2               | Functional Description                                   | .5 |

|   | 1.2               | 2.1 Sensing element                                      | .5 |

|   | 1.2.              | 2.2 Interface IC                                         | .5 |

|   | 1.2               | 2.3 Factory calibration                                  | .6 |

|   | 1.2.              |                                                          |    |

|   | 1.2               |                                                          |    |

|   |                   | .2.5.1 High resolution measurement                       |    |

|   |                   | .2.5.2 High speed measurement                            |    |

|   |                   | .2.5.3 Ultra low power measurement                       |    |

|   |                   | .2.5.4 Low power measurement with external trigger       |    |

|   | 1                 | .2.5.5 Temperature output                                | .6 |

| 2 | Sta               | art-up, Operation Modes, HW functions and Clock          | 7  |

|   |                   |                                                          |    |

|   | 2.1               | Start-up                                                 |    |

|   |                   | .2 SCP1000 initialization during start-up (Phase 1)      |    |

|   |                   | 2.1.2.1 SCP1000 initialization during start-up (Phase 2) |    |

|   |                   | 2.1.2.2 SCP1000 checksum error check (optional)          |    |

|   |                   | .3 SCP1000 low noise configuration (Phase 3)             |    |

|   | 2.1.              |                                                          |    |

|   | 2.2               |                                                          |    |

|   | 2.2.              | ···· · · · · · · · · · · · · · · · · ·                   |    |

|   |                   | 2.2.1.1 Continuous measurement modes                     |    |

|   |                   | 2.2.1.2 Triggered (low power) measurement mode           |    |

|   |                   | .2 Measurement mode selection                            |    |

|   |                   | 2.2.2.1 Switching between measurement modes              | 11 |

|   |                   | .3 Reading the pressure and temperature                  |    |

|   |                   | 2.2.3.1 Examples of temperature conversion to [°C]       |    |

|   | 2.2               |                                                          |    |

|   |                   | 2.2.4.1 High resolution measurement mode                 |    |

|   | _                 | P.2.4.2 High speed measurement mode                      |    |

|   |                   | 2.2.4.3 Ultra low power measurement mode                 |    |

|   | 2                 | 2.2.4.4 Low power measurement mode                       |    |

|   | 2.3               | Over Pressure Detection                                  | 16 |

|   | 2.4               | DRDY – data ready pin                                    | 16 |

|   | 2.5               | TRIG – trigger pin                                       | 16 |

|   | 2.6               | Power Down Mode and PD Pin                               |    |

|   | <b>2.0</b><br>2.6 |                                                          |    |

|   | 2.0.              |                                                          |    |

|   |                   |                                                          |    |

|   | 2.7               | Standby Mode                                             | 17 |

|   | 2.8               | Reset                                                    | 17 |

|   | 2.9               | Clock                                                    | 17 |

|   |                   |                                                          |    |

| 3 | Ado               | dressing Space                                           | 18 |

|   | 3.1               | Register Description                                     | 18 |

|   | 3.2 | Direct Access Registers                               | 18 |

|---|-----|-------------------------------------------------------|----|

|   | 3.3 | Indirect Access Registers                             | 21 |

|   | 3.3 | -                                                     |    |

|   | 3.4 | EEPROM memory                                         | 22 |

|   | 3.4 | J                                                     |    |

|   | 3.4 | .2 EEPROM reading                                     | 23 |

| 4 | Ser | rial Interfaces                                       | 24 |

|   | 4.1 | SPI Interface                                         | 24 |

|   | 4.1 |                                                       |    |

|   | 4.1 | j                                                     |    |

|   |     | .1.2.1 MISO line configured to open drain drive state |    |

|   |     | .3 Examples of SPI communication                      |    |

|   |     | TWI Interface                                         |    |

|   |     | .1 TWI frame format                                   |    |

|   |     | .2.1.1 TWI write sequence                             |    |

|   |     | .2.1.2 8 bit TWI read sequence                        |    |

|   | 4   | .2.1.3 16 bit TWI read sequence                       | 29 |

| 5 | Ele | ctrical Characteristics                               | 31 |

| : | 5.1 | Absolute Maximum Ratings                              | 31 |

|   | 5.2 | Power Supply                                          | 31 |

|   | 5.3 | Digital I/O Specification                             | 31 |

|   | 5.3 | .1 Digital I/O characteristics                        | 31 |

|   | 5.3 |                                                       |    |

|   | 5.3 | .3 TWI AC characteristics                             | 33 |

| 6 | Pad | ckage Characteristics                                 | 34 |

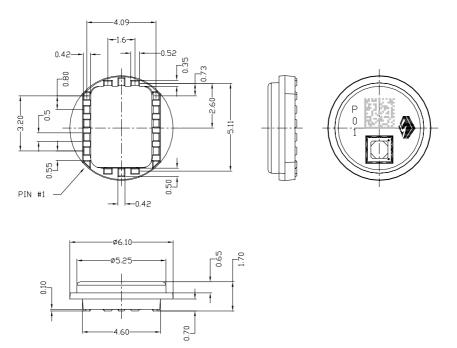

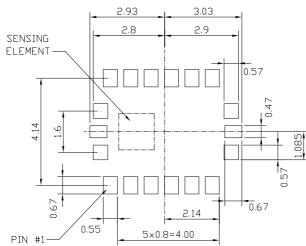

|   | 6.1 | Dimensions                                            | 34 |

| 7 | Ар  | plication Information                                 | 35 |

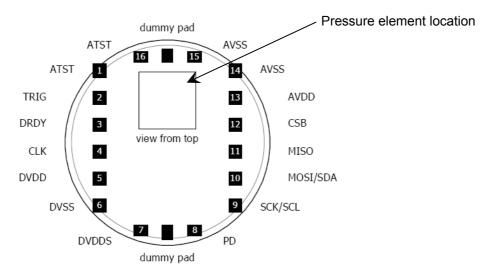

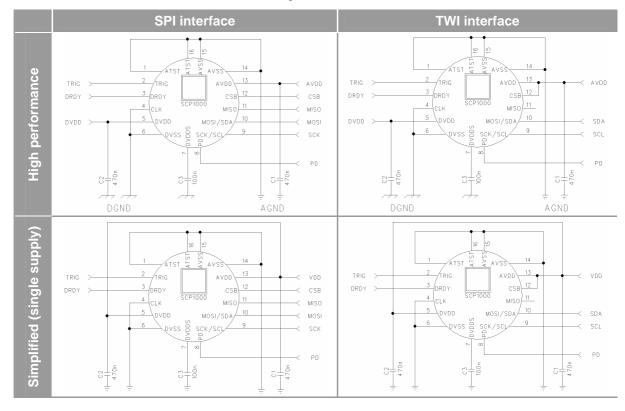

|   | 7.1 | Pin Description                                       | 35 |

|   | 7.2 | Recommended Circuit Diagrams                          | 36 |

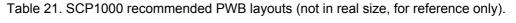

|   | 7.3 | Recommended PWB Layout                                | 36 |

|   | 7.4 | Assembly instructions                                 |    |

|   | 7.5 | Tape and reel specifications                          |    |

| 8 | Do  | cument Revision History                               | 39 |

|   |     |                                                       |    |

| 9 | Co  | ntact Information                                     | 39 |

#### **1** General Description

#### 1.1 Introduction

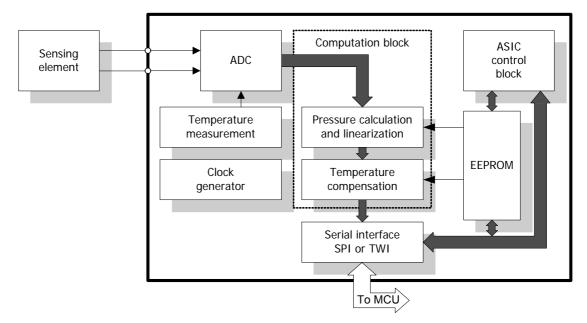

SCP1000 is pressure sensor that measures absolute pressure. The sensor consists of a silicon bulk micro machined sensing element chip and a signal conditioning ASIC. The pressure sensor element and the ASIC are mounted inside a plastic pre-moulded package and wire bonded to appropriate contacts. The round shaped sensor component has 18 SMD solderable contacts. SCP1000 block diagram is presented in Figure 1 below.

Figure 1. SCP1000 system level block diagram.

#### **1.2 Functional Description**

The SCP1000 performs almost complete data processing on-chip. The pressure and temperature output data are calibrated and compensated internally. The only operations over the output data required to obtain the pressure in [Pa] and the temperature in [°C] is single multiplication with constants, see more details in section 2.2.3.

#### 1.2.1 Sensing element

The sensing element is manufactured using the proprietary bulk 3D-MEMS process of VTI enabling robust, stable, low noise and low power capacitive sensors.

Absolute pressure sensor element consists of a silicon wafer that is locally thinned to form a pressure sensitive diaphragm. The diaphragm acts as a movable plate of the capacitive sensor. The stationary plate is a thin film metal deposited on a second, glass coated silicon wafer. The wafers are joined by anodic bonding so that a hermetically enclosed space is formed between them. The diaphragm deflects due to the pressure difference between the exterior of the sensor and the internal vacuum reference chamber.

#### 1.2.2 Interface IC

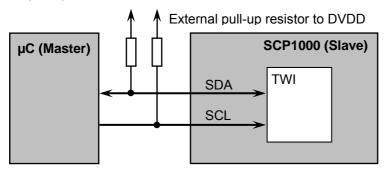

The communication between the SCP1000 and its host micro-controller ( $\mu$ C) is based on a serial interface, an interrupt line and specialized pins used to trigger special functions. The serial interface allows registers' read and write operations and the interrupt line signals events, which require host intervention. Two different serial interfaces are available: SPI and TWI (TWI is very similar to I<sup>2</sup>C bus). The appropriate communication interface is pre-programmed in the factory. The register access protocol is independent on the selected interface.

#### 1.2.3 Factory calibration

All sensors are factory calibrated. Some of the calibration parameters are: sensitivity to pressure, offset, temperature sensitivity and temperature compensation. Calibration parameters will be read automatically from the internal non-volatile during the start-up of the sensor.

#### **1.2.4 Supported features**

SCP1000 different versions and supported features are presented in Table 1 below.

Table 1. SCP1000 versions.

| Features                       | SCP1000-D01     | SCP1000-D11     |

|--------------------------------|-----------------|-----------------|

| Supply voltage                 | 2.4 V – 3.3 V   | 2.4 V – 3.3 V   |

| Measuring range                | 30 kPa – 120kPa | 30 kPa – 120kPa |

| Resolution <sup>1</sup>        | 1.5 Pa          | 1.5 Pa          |

| Interface                      | SPI max 500 kHz | TWI max 400 kHz |

| Temperature output             | Yes             | Yes             |

| Clock                          | Internal        | Internal        |

| Marking on top of<br>component | P01             | P03             |

<sup>1</sup> typical value in high resolution measurement mode

#### 1.2.5 Operation

The SCP1000 pressure sensor has 4 measurement modes plus standby and power down mode. In all measurement modes, the pressure output word-length is 19 bits and the temperature output word-length is 14 bits.

#### **1.2.5.1** High resolution measurement

In the high-resolution measurement mode the pressure is measured continuously with the highest resolution and the output data refresh rate is typically 1.8 Hz.

#### 1.2.5.2 High speed measurement

In the high speed measurement mode the measurements are performed continuously as well and the conversion time is shortened at the cost of output resolution. This allows for an increase of the output data refresh rate up approximately 9 Hz.

#### 1.2.5.3 Ultra low power measurement

In the ultra low power measurement mode the device performs periodic measurements with the lowest resolution (15 bits) and switches to standby mode between the measurements. In this mode the updated pressure data is available approximately once per second.

#### 1.2.5.4 Low power measurement with external trigger

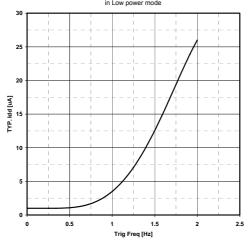

In the low power measurement mode the device stays in standby mode and is ready to perform single measurement using the selected resolution, 15 bits or 17 bits. After the measurement is complete and the output data is refreshed, the sensor switches back to standby mode. Average current consumption in low power mode depends on measurement resolution and trigger frequency.

#### 1.2.5.5 Temperature output

Temperature information is available in every measurement mode for each pressure measurement.

# 2 Start-up, Operation Modes, HW functions and Clock

#### 2.1 Start-up

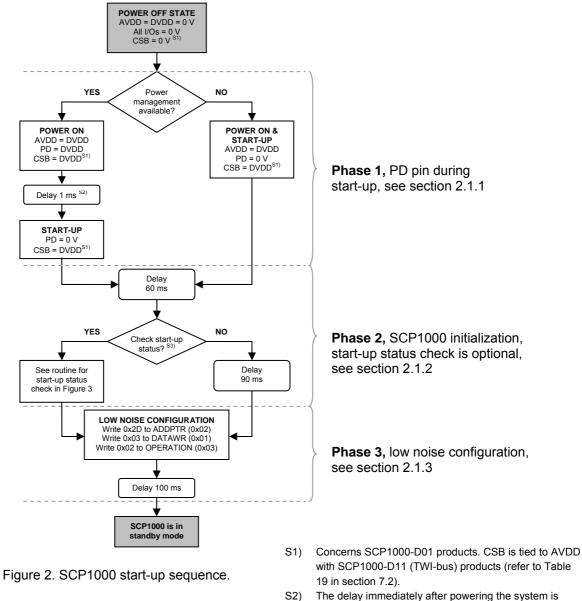

The SCP1000 initialization sequence described in this section (and in Figure 2) is performed each time the sensor is:

- powered up,

- waking up from power down mode

- waking up after reset.

During the start-up the power supplies must stabilize in to specified range before configuration and calibration data can be loaded from the non-volatile memory to volatile registers. The start-up sequence is divided into 3 phases described below in Figure 2.

- S2) The delay infinediately after powering the system is needed in order to let the power supply and the voltage over the filter capacitors to stabilize. If it is needed this delay time can be increased.

- S3) Status check is optional, see section 2.1.2.

#### 2.1.1 Power down-pin (PD) during start-up (Phase 1)

SCP1000 has an external power down (PD) pin. In case the system has power management capabilities, it is recommended that during power up the PD pin is tied to DVDD – this way the sensor is forced to remain in power down mode during the stabilization of the power supplies. After approximately 1ms (or longer depending on the power supply stabilization time) the PD pin can be switched to DVSS allowing the sensor to start the power up and the initialization procedure to begin.

In case the system does not have power management capability the PD pin can be tied to DVSS.

#### 2.1.2 SCP1000 initialization during start-up (Phase 2)

A 60 ms delay after the start-up (Phase 1 in Figure 2) is recommended. After the delay initialization will be finished and all configuration registers are loaded with their default values. During the 60 ms start-up delay there should not be any interface activity attempts.

Start-up status check is optional and can be replaced with 90 ms delay, see Figure 2.

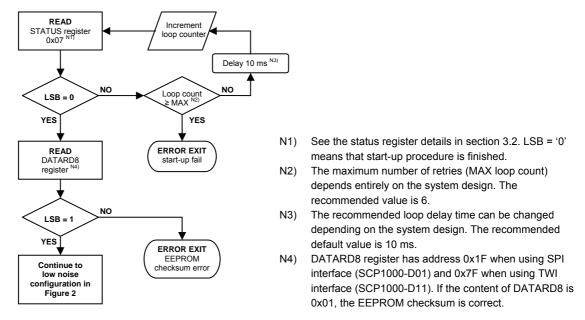

The start-up status check includes EEPROM checksum error result check. The routine is described in Figure 3 and in sections 2.1.2.1 and 2.1.2.2 below.

Figure 3. Routine for start-up status check (optional).

#### 2.1.2.1 SCP1000 initialization status check (optional)

The STATUS register 0x07 (see Figure 3) can be read to verify that start-up procedure is finished. If the STARTUP bit (LSB) of the STATUS register (0X07) is '0', the start-up procedure is finished successfully. If the STARTUP bit of the STATUS register is '1', the start-up procedure is still running.

If the start-up procedure is still running, it is advised to re-check the STATUS register after a delay. A recommend delay is 10ms. If the start-up procedure is not finished after the additional delay, the re-check procedure can be started again (see Figure 3). In order to avoid infinite loop in case of sensor malfunction it is advisable to limit the maximum number of cycles. Recommended value is 6 cycles when using 10 ms additional delay. If the start-up procedure is not finished successfully after the maximum number of STATUS register re-check cycles has expired, the start-up procedure has failed.

#### 2.1.2.2 SCP1000 checksum error check (optional)

The DATARD8 register (address 0x1F when using SPI interface or 0x7F when using TWI interface) can be read in order to check the EEPROM checksum error (see Figure 3). If the content of DATARD8 is 0x00, EEPROM checksum calculation indicated an error and the start-up procedure is failed. Correct EEPROM checksum calculation result is indicated by content of 0x01 in DATARD8.

#### 2.1.3 SCP1000 low noise configuration (Phase 3)

SCP1000 is needs to be configured for low noise operation (Phase 3 in Figure 2). After low noise configuration the start-up sequence is completed and SCP1000 is in standby mode, see section 2.2 for details of measurement mode activation.

#### 2.2 Measurement Modes

SCP1000 pressure sensor measurement modes are presented in Table 2 below. In three of the measurement modes SCP1000 samples pressure and temperature continuously. In low power mode SCP1000 measures pressure and temperature once after the measurement is triggered.

| Measurement mode | Activation code  | Resolution         | Measurement<br>type |

|------------------|------------------|--------------------|---------------------|

| High resolution  | 0x0A             | 17 bits            | Continuous          |

| High speed       | 0x09             | 15 bits            | Continuous          |

| Ultra low power  | 0x0B             | 15 bits            | Continuous          |

| Low power        | 0x0C or TRIG pin | 17 bits or 15 bits | Triggered           |

Table 2. SCP1000 measurement modes.

#### 2.2.1 Measurement modes timing and real time constraints

#### 2.2.1.1 Continuous measurement modes

In continuous measurement mode the output data is refreshed after each measurement and the availability of the updated pressure and temperature data is signaled through the assertion of the DRDY pin and a DRDY bit is set to '1' in the STATUS register.

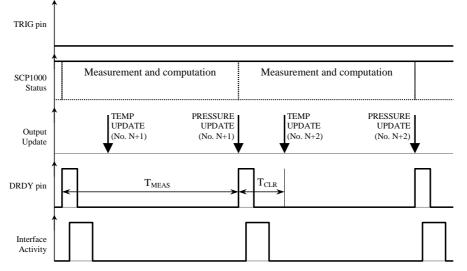

In Figure 4 is presented the timing diagram in the continuous measurement modes.

Figure 4. Timing diagram in continuous measurement mode.

In order to clear the DRDY signal, the host processor has to read the pressure output data. The temperature output data is updated before the pressure output data, thus the time to service the DRDY ( $T_{CLR}$  in Figure 4) is shorter than the measurement and computation time ( $T_{MEAS}$  in Figure 4).

In the case that the temperature data is not needed, the time for servicing the DRDY interrupt can be extended. In any case, the DRDY interrupt must be serviced (the pressure data reading has to be completed) before the next pressure data update.

If, for some reason, the real time requirement is not met, the output data will be overwritten and an RTERR error bit is set to '1' in the STATUS register. In order to clear the error status, the host processor has to read the output pressure data (this data can be invalid). Once the error has been cleared, normal operation can be continued.

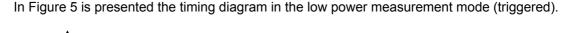

#### 2.2.1.2 Triggered (low power) measurement mode

In triggered measurement mode (low power) SCP1000 stays in standby mode until measurement is externally triggered, see section for more 2.2.4.4 details. The availability of updated pressure and temperature data is signaled as in continuous measurement modes (through the assertion of the DRDY pin and a DRDY bit is set to '1' in the STATUS register).

Figure 5. Timing diagram in triggered measurement mode.

See section 2.2.1.1 for details of clearing the DRDY signal and avoiding real time error.

The DRDY interrupt request has to be cleared before the next trigger signal is applied (rising edge at TRIG pin Figure 5).

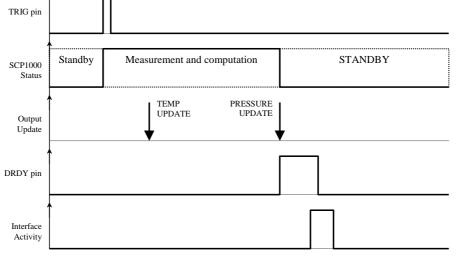

#### 2.2.2 Measurement mode selection

The selection and activation of the measurement mode is done by writing the corresponding mode activation code (see Table 2) in to OPERATION register, see section 3.2 for register details. The measurement mode selection and activation is illustrated in Figure 6 below.

- M1) For details for low power mode resolution please refer to section 2.2.1.2.

- M2) For details for DRDY signal please see Figure 4, Figure 5 and section 2.4.

- M3) See section 2.2.3 for more details of reading the pressure and temperature

Figure 6. SCP1000 measurement mode selection.

#### 2.2.2.1 Switching between measurement modes

In order to switch between the measurement modes, it is necessary first to stop the active mode before activating the new one by writing 0x00 in to OPERATION register. This will instruct SCP1000 to cancel the current operation (SCP1000 enters in to standby mode). After writing 0x00 to OPERATION register and before new measurement mode is activated there should be a 50 ms delay. Instead of the 50 ms delay, OPSTATUS register can be read. If OPSTATUS bit in OPSTATUS register is '0', new measurement mode can be activated as described in section 2.2.2 above (see Figure 6).

In order to avoid a real time error, it is strongly recommended to verify that the DRDY signal is low (no new data) before activating new mode. If DRDY is high it is necessary to read the output data before activating new measurement mode.

#### 2.2.3 Reading the pressure and temperature

After the DRDY pin has signaled the availability of new measurement data, it is recommended that the output data is read immediately in the following order:

- read the TEMPOUT register (temperature data in bits [13:0] in case the temperature data is not needed this step can be omitted).

- o read the DATARD8 register (bits [2:0] contain the MSB of the pressure data)

o read the DATARD16 register (contains the 16 LSB of the pressure data)

See section 3.2 (Table 12) for more details of pressure data bit level description. Pressure data is presented in integer format and is converted from decimal format to [Pa] as follows: Equation 1

$$Pres[Pa] = \frac{Pres[dec]}{4} = 0.25 \cdot Pres[dec],$$

where Pres[dec] is pressure read from SCP1000 in decimal format.

See section 3.1 (Table 13) for details more of temperature data bit level description. Temperature data is presented in 2's complement format and is converted from decimal format to [ $^{\circ}$ C] as follows:

Equation 2

$$Temp[^{\circ}C] = \frac{Temp[dec]}{20} = 0.05 \cdot Temp[dec]$$

where *Temp[dec]* is temperature read from SCP1000 in decimal format.

#### 2.2.3.1 Examples of temperature conversion to [°C]

In case the sign bit is zero, '0' (see Table 3), the TEMPOUT binary value is converted to decimal value and then to [ $^{\circ}$ C] as follows:

Table 3. An example TEMPOUT bit pattern of a positive temperature data.

|                  |     | An example TEMPOUT bit pattern for positive temperature |     |       |       |      |      |      |     |     |     |     |     |     |     |      |

|------------------|-----|---------------------------------------------------------|-----|-------|-------|------|------|------|-----|-----|-----|-----|-----|-----|-----|------|

| Bit#             | B15 | B14                                                     | B13 | B12   | B11   | B10  | B9   | B8   | B7  | B6  | B5  | B4  | B3  | B2  | B1  | B0   |

| ~[°C]            |     |                                                         | s   | 204.8 | 102.4 | 51.2 | 25.6 | 12.8 | 6.4 | 3.2 | 1.6 | 0.8 | 0.4 | 0.2 | 0.1 | 0.05 |

| Data<br>bit #    | x   | x                                                       | s   | T12   | T11   | T10  | Т9   | Т8   | Τ7  | Т6  | T5  | T4  | Т3  | T2  | T1  | Т0   |

| TEMPC<br>raw dat | a   |                                                         | 0   | 0     | 0     | 0    | 1    | 0    | 0   | 0   | 1   | 0   | 1   | 1   | 1   | 0    |

s = sign bitx = not used bit

The example binary value presented in Table 3 can be converted normally to decimal value because the sign bit is zero:

bin '00 0010 0010 1110'  $\rightarrow$  dec '558'  $\rightarrow$  conversion to [°C]: 558/20 = 27,9 °C

In case the sign bit is one, '1' (see Table 4), the TEMPOUT binary value is converted to decimal value and then to [ $^{\circ}$ C] as follows (notice 2's complement format):

Table 4. An example TEMPOUT bit pattern of a negative temperature data.

|                                               |       | An example TEMPOUT bit pattern for negative temperature |     |       |       |      |      |      |     |     |     |     |     |     |     |      |

|-----------------------------------------------|-------|---------------------------------------------------------|-----|-------|-------|------|------|------|-----|-----|-----|-----|-----|-----|-----|------|

| Bit#                                          | B15   | B14                                                     | B13 | B12   | B11   | B10  | B9   | B8   | B7  | B6  | B5  | B4  | B3  | B2  | B1  | B0   |

| ~[°C]                                         |       |                                                         | S   | 204.8 | 102.4 | 51.2 | 25.6 | 12.8 | 6.4 | 3.2 | 1.6 | 0.8 | 0.4 | 0.2 | 0.1 | 0.05 |

| Data<br>bit #                                 | х     | х                                                       | s   | T12   | T11   | T10  | Т9   | Т8   | Τ7  | Т6  | T5  | T4  | Т3  | T2  | T1  | Т0   |

| TEMPC<br>raw da                               | ,     |                                                         | 1   | 1     | 1     | 1    | 1    | 1    | 1   | 0   | 0   | 1   | 0   | 1   | 0   | 0    |

| TEMPOUT,<br>inverted data                     |       |                                                         | 0   | 0     | 0     | 0    | 0    | 0    | 0   | 1   | 1   | 0   | 1   | 0   | 1   | 1    |

| Add '1' (one LSB) to inverted<br>TEMPOUT data |       |                                                         |     |       |       |      | +1   |      |     |     |     |     |     |     |     |      |

| Absolute value for<br>TEMPOUT data            |       |                                                         | 0   | 0     | 0     | 0    | 0    | 0    | 0   | 1   | 1   | 0   | 1   | 1   | 0   | 0    |

| s = sia                                       | n hit |                                                         |     |       |       |      |      |      |     |     |     |     |     |     |     |      |

s = sign bit x = not used bit

The raw TEMPOUT data (bin '11 1111 1001 0100') is not converted to decimal value because the sign bit is '1'. The bit pattern is first inverted (bin '00 0000 0110 1011') and then 1 LSB is added to the inverted bit pattern. The resulting bit pattern is presented in the last row of Table 4 (Absolute value for TEMPOUT data), which is converted normally to decimal value:

bin '00 0000 0110 1100'  $\rightarrow$  dec '108'  $\rightarrow$  dec '-108' (because sign bit is '1')  $\rightarrow$  conversion to [°C]: -108/20 = -5,4 °C

#### 2.2.4 Measurement mode details

In this section all measurement modes are described in detail.

#### 2.2.4.1 High resolution measurement mode

In high resolution measurement mode pressure and temperature are measured continuously with the highest resolution. High resolution mode is activated by writing 0x0A in to OPERATION register. Once the mode has been started the only interface activity required is periodic reading of the output pressure and temperature registers (in applications where the temperature is not needed the output temperature reading can be omitted), see section 2.2.1.1.

SCP1000 operation parameters in high resolution measurement mode are presented in Table 5 below.

| Symbol            | Parameter                                        | Min | Тур | Max | Unit |

|-------------------|--------------------------------------------------|-----|-----|-----|------|

| V <sub>dd</sub>   | Supply voltage (AVDD & DVDD)                     | 2.4 | 2.7 | 3.3 | V    |

| l <sub>dd</sub>   | Average supply current                           |     | 25  |     | μA   |

| P <sub>res</sub>  | Pressure measurement resolution                  |     | 17  |     | bits |

| T <sub>res</sub>  | Temperature measurement resolution               | -   | 14  | -   | bits |

| PWL               | Pressure data output word-length                 | -   | 19  | -   | bits |

| TWL               | Temperature data output word-<br>length          | -   | 14  | -   | bits |

| T <sub>meas</sub> | Measurement and computation time                 |     | 500 |     | ms   |

| F <sub>meas</sub> | Output data refresh rate                         | 1.6 | 1.8 | 2.0 | Hz   |

| T <sub>clr</sub>  | Maximum time for servicing the<br>DRDY interrupt |     | 55  |     | ms   |

Table 5. SCP1000 operation parameters in high resolution mode.

#### 2.2.4.2 High speed measurement mode

In high speed measurement mode pressure and temperature are measured continuously the conversion time is shortened at the cost of output resolution. This allows an increased output refresh rate of approximately 9 Hz.

SCP1000 operation parameters in high speed measurement mode are presented in Table 6 below.

Table 6. SCP1000 operation parameters in high speed mode.

| Symbol            | Parameter                                        | Min | Тур | Max  | Unit |

|-------------------|--------------------------------------------------|-----|-----|------|------|

| V <sub>dd</sub>   | Supply voltage (AVDD & DVDD)                     | 2.4 | 2.7 | 3.3  | V    |

| l <sub>dd</sub>   | Average supply current                           |     | 25  |      | μA   |

| P <sub>res</sub>  | Pressure measurement resolution                  |     | 15  |      | bits |

| T <sub>res</sub>  | Temperature measurement resolution               | -   | 14  | -    | bits |

| PWL               | Pressure data output word-length                 | -   | 19  | -    | bits |

| TWL               | Temperature data output word-<br>length          | -   | 14  | -    | bits |

| T <sub>meas</sub> | Measurement and computation time                 |     | 140 |      | ms   |

| F <sub>meas</sub> | Output data refresh rate                         | 7.9 | 9   | 10.2 | Hz   |

| T <sub>clr</sub>  | Maximum time for servicing the<br>DRDY interrupt |     | 25  |      | ms   |

#### 2.2.4.3 Ultra low power measurement mode

In ultra low power measurement mode the device performs measurements continuously with the lowest resolution (15 bits) and switches to standby mode between measurements. In this mode the updated pressure data is available approximately once per second. The average current consumption is in the range of  $3.5 \ \mu$ A.

SCP1000 operation parameters in ultra low power measurement mode are presented in Table 7 below.

|  | Table 7. | SCP1000 c | peration | parameters i | n ultra | low power mode |  |

|--|----------|-----------|----------|--------------|---------|----------------|--|

|--|----------|-----------|----------|--------------|---------|----------------|--|

| Symbol            | Parameter                                        | Min | Тур | Max | Unit |

|-------------------|--------------------------------------------------|-----|-----|-----|------|

| V <sub>dd</sub>   | Supply voltage (AVDD & DVDD)                     | 2.4 | 2.7 | 3.3 | V    |

| I <sub>dd</sub>   | Average supply current                           |     | 3.5 |     | μA   |

| P <sub>res</sub>  | Pressure measurement resolution                  |     | 15  |     | bits |

| T <sub>res</sub>  | Temperature measurement resolution               | -   | 14  | -   | bits |

| PWL               | Pressure data output word-length                 | -   | 19  | -   | bits |

| TWL               | Temperature data output word-<br>length          | -   | 14  | -   | bits |

| F <sub>meas</sub> | Output data refresh rate                         |     | 1   |     | Hz   |

| T <sub>clr</sub>  | Maximum time for servicing the<br>DRDY interrupt |     | 500 |     | ms   |

#### 2.2.4.4 Low power measurement mode

In low power measurement mode SCP1000 stays in standby mode until measurement is externally triggered. The measurement is triggered with rising edge of TRIG pin or by writing 0x0C to OPERATION register. Low power measurement can be triggered after start-up and power down. If some other measurement mode is activated, see section 2.2.2.1 for details of switching between measurement modes.

The default measurement resolution for low power mode is 17 bits. Resolution can be configured to 15 bit or 17 bit mode through indirect CFG register (see section 3.3). The CFG register contents are presented in Table 8 below.

Table 8. Recommended CFG register contents.

| Resolution        | CFG register content |

|-------------------|----------------------|

| 17 bits (default) | 0x05                 |

| 15 bits           | 0x0D                 |

SCP1000 operation parameters in low power measurement mode are presented in Table 9 below.

| Symbol            | Parameter                                        | Min  | Ту                              | /p       | Max   | Unit |

|-------------------|--------------------------------------------------|------|---------------------------------|----------|-------|------|

| Cymbol            | 1 didition                                       |      | 15 bits                         | 17 bits  | max   | Onic |

| $V_{dd}$          | Supply voltage (AVDD & DVDD)                     | 2.4  | 2.                              | 7        | 3.3   | V    |

| l <sub>dd</sub>   | Average supply current                           | 1    | Depen<br>resoluti<br>trigger fr | on and   | 25    | μA   |

| P <sub>res</sub>  | Pressure measurement resolution                  |      | 15                              | 17       |       | bits |

| T <sub>res</sub>  | Temperature measurement resolution               | -    | 1.                              | 4        | -     | bits |

| PWL               | Pressure data output word-length                 | _    | 1                               | 9        | -     | bits |

| TWL               | Temperature data output word-<br>length          | -    | 1.                              | 4        | -     | bits |

| T <sub>meas</sub> | Measurement and computation time                 |      | 140                             | 500      |       | ms   |

| F <sub>trig</sub> | Maximum trigger frequency                        |      | 9                               | 1.8      |       | Hz   |

| T <sub>clr</sub>  | Maximum time for servicing the<br>DRDY interrupt | Befo | re the ne>                      | t TRIG s | ignal | -    |

Table 9. SCP1000 operation parameters in low power mode.

Typical SCP1000 Current Consumption vs. Ext trigger frequency in Low power mode

Figure 7. Typical current consumption in low power mode with 17 bit resolution.

#### 2.3 Over Pressure Detection

When operating within the nominal operation range (30...120 kPa) the output of the SCP1000 changes between 120000 and 480000. In the case of major overpressure (P > 250 kPa) SCP1000 provides a warning by setting the bit OVP bit to '1' in the STATUS register.

It is recommended in applications where over pressure situations may occur and when operating close to the upper limit of the operation range, that the STATUS register is read each time when a pressure reading is made and the OVP bit is checked. In major over pressure situations, a sudden drop of the output reading can be observed. If regular reading of the STATUS register is not performed, it is recommended that the OVP status is checked in order to verify the pressure reading in situations when the output drops rapidly.

#### 2.4 DRDY – data ready pin

Availability of updated pressure and temperature data is signaled through the assertion of the DRDY pin. DRDY is cleared after the DATARD16 register is read, see section 2.2.1 for more detailed information.

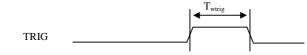

#### 2.5 TRIG – trigger pin

TRIG pin is used to trig the measurement in low power measurement mode (external trigger). The  $\mu$ C has to actively drive the signal in high and low states. In applications where the TRIG signal is not used it has be connected to DVSS. See section 2.2.4.4 for more detailed information.

#### 2.6 Power Down Mode and PD Pin

In order to decrease further the current consumption in cases where there are long time intervals between the measurements, SCP1000 has a built in power down mode, which can be activated through the PD pin. SCP1000 will stay in power down mode as long as the PD signal is high.

After PD signal changes back to low, SCP1000 powers up, performs initialization and is ready to operate. Start-up sequence has to be executed always after power down mode, see section 2.1 for more detailed information.

The advantage of using power down mode instead of switching off the supply is that during wakeup from power down there is no need to recharge the filter capacitors on AVDD and DVDD lines. The  $\mu$ C has to actively drive the signal in high and low states. In applications where the PD signal is not used it has to be connected to DVSS.

The current consumption of SCP1000 in power down mode is typically 0.2 µA.

#### 2.6.1 Power down mode with SCP1000-D11

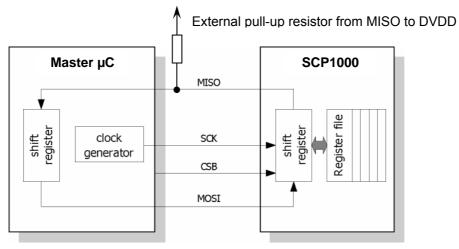

SCP1000-D11 is operated with TWI bus. When the SCP1000-D11 is set in to power down mode, instead of tri-stating, the SDA pin will drive its output actively to zero. Since the SDA pin (MOSI/SDA) requires an external pull up resistor from SDA to DVDD (see Figure 12 section 4.2), the power consumption is increased by the power driven through the external pull up resistor from DVDD to GND.

#### 2.6.2 Power down mode with SCP1000-D01 in open drain configuration

SCP1000-D01 is operated with SPI bus and can be configured to open drain drive state, see section 4.1.2. When the SCP1000-D01 is set in to power down mode, instead of tri-stating, the MISO pin will drive its output actively to zero. Since the MISO pin requires an external pull up resistor in open drain drive state (see Figure 10 section 4.1.2.1), the power consumption is increased by the power driven through the external pull up resistor from DVDD to GND.

#### 2.7 Standby Mode

SCP1000 is in standby mode after start-up, when OPERATION register content is 0x00 and in ultra low power measurement mode between the measurements. The average current consumption is in the range of 1  $\mu$ A.

#### 2.8 Reset

SCP1000 ASIC software can be reseted by writing 0x01 in to RSTR register. After reset the RSTR register content is set to 0x00 and the default values are loaded from EEPROM. The start-up sequence should be followed from section 2.1.2 onwards after reset.

#### 2.9 Clock

The SCP1000 pressure sensor is operated with internal clock, so external clock signal is not needed.

#### 3 Addressing Space

SCP1000 register contents and bit definitions are described in more detail in next sections. All registers are read and written through the serial host interface.

#### 3.1 Register Description

SCP1000 register types:

- direct access registers,

- indirect access registers and

- EEPROM registers.

Table 10. List of SCP1000 direct and indirect access registers and EEPROM registers.

| A<br>SPI | Address<br>TWI | Name      | Description                                                             | Mode            | Register<br>access | Width[<br>bits] |

|----------|----------------|-----------|-------------------------------------------------------------------------|-----------------|--------------------|-----------------|

|          | 0x00           | REVID     | ASIC revision number                                                    | (R, W, RW)<br>R | Direct             | 8               |

|          | 0x01           | DATAWR    | Indirect register access data                                           | RW              | Direct             | 8               |

|          | 0x02           | ADDPTR    | Indirect register access pointer                                        | RW              | Direct             | 8               |

|          | 0x03           | OPERATION | Operation register                                                      | RW              | Direct             | 8               |

|          | 0x04           | OPSTATUS  | Operation status                                                        | R               | Direct             | 8               |

|          | 0x06           | RSTR      | ASIC software reset                                                     | W               | Direct             | 8               |

|          | 0x07           | STATUS    | ASIC top-level status                                                   | R               | Direct             | 8               |

| 0x1F     | 0x7F           | DATARD8   | Pressure output data (MSB) or 8 bit data read from EEPROM               | R               | Direct             | 8               |

| 0x20     | 0x80           | DATARD16  | Pressure output data (LSB) or<br>8-bit data read from indirect register | R               | Direct             | 16              |

| 0x21     | 0x81           | TEMPOUT   | 14-bit temperature output data                                          | R               | Direct             | 16              |

|          | 0x00           | CFG       | Configuration register                                                  | RW              | Indirect           | 8               |

|          | 0x05           | TWIADD    | TWI address                                                             | W               | Indirect           | 8               |

|          | 0x09           | CFG2      | MISO configuration,<br>only for SCP1000-D01                             | RW              | Indirect           | 8               |

|          | 0x2D           | MODTEST2  | Noise level configuration                                               | W               | Indirect           | 8               |

|          | 0x29           | USERDATA1 | User data                                                               | RW              | EEPROM             | 8               |

|          | 0x2A           | USERDATA2 | User data                                                               | RW              | EEPROM             | 8               |

|          | 0x2B           | USERDATA3 | User data                                                               | RW              | EEPROM             | 8               |

|          | 0x2C           | USERDATA4 | User data                                                               | RW              | EEPROM             | 8               |

Register address in hex format.

RW – Read / Write register, R – Read only register.

#### 3.2 Direct Access Registers

SCP1000 direct access register contents and bit definitions are described in this section. Direct access registers can be accessed directly through the serial interface.

#### Address: 0x00

Register name: REVID, ASIC revision number

| Bits | Mode | Initial<br>Value | Name  | Description          |

|------|------|------------------|-------|----------------------|

| 7:0  | R    | 01h              | REVID | ASIC revision number |

#### Address: 0x01

Register name: DATAWR, indirect register data

| Bits | Mode | Initial<br>Value | Name | Description          |

|------|------|------------------|------|----------------------|

| 7:0  | WR   | 00h              | DATA | Indirect access data |

#### Address: 0x02

Register name: **ADDPTR**, indirect register address (address pointer)

| Bits | Mode | Initial<br>Value | Name | Description               |

|------|------|------------------|------|---------------------------|

| 7:0  | WR   | 00h              | ADDR | Indirect register address |

#### Address: 0x03

| Register name: <b>OPERATION</b> , o | operation register |

|-------------------------------------|--------------------|

|-------------------------------------|--------------------|

| Bits | Mode | Initial<br>Value | Name      | Description                            |

|------|------|------------------|-----------|----------------------------------------|

| 7:0  | WR   | 00h              | OPERATION | See operation description in Table 11. |

Table 11. Description for register contents in OPERATION register.

| Operation | Description                                                                                                                                                                                    |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x00      | No operation / cancel current operation (standby mode). Default value after start-up, power down mode and reset.                                                                               |

| 0x01      | Read indirect access register pointed by ADDPTR. Register contents is available in DATARD16 in bits [7:0].                                                                                     |

| 0x02      | Write DATAWR contents in to the indirect access register pointed by<br>ADDPTR.                                                                                                                 |

| 0x05      | Read EEPROM register pointed by ADDPTR. Register contents is available in DATARD8 in bits [7:0].                                                                                               |

| 0x06      | Write DATAWR contents in to the EEPROM register pointed by ADDPTR.                                                                                                                             |

| 0x07      | Perform INIT sequence: INIT values are downloaded from the EEPROM to the processing unit. After the INIT sequence is over the INIT status is present at DATARD8:<br>- DATARD8 = 0x01 → success |

|           | - DATARD8 = $0x00 \rightarrow fail - checksum error$                                                                                                                                           |

| 0x09      | High speed acquisition mode start (continuous measurement).<br>Use operation 0x00 to stop the continuous acquisition                                                                           |

| 0x0A      | High resolution acquisition mode start (continuous measurement).<br>Use operation 0x00 to stop the continuous acquisition                                                                      |

| 0x0B      | Ultra low power acquisition mode start (continuous measurement).<br>Use operation 0x00 to stop the continuous acquisition                                                                      |

| 0x0C      | Low power acquisition start (perform single temperature and pressure measurement, equivalent to external TRIG pin)                                                                             |

| 0x0F      | <ul> <li>ASIC self test. After the self test is over the result is present at DATARD8:</li> <li>DATARD8 = 0x01 → self test successful</li> <li>DATARD8 = 0x00 → self test failed</li> </ul>    |

| Others    | Reserved                                                                                                                                                                                       |

# Address: 0x04

Register name: **OPSTATUS**, operation status

| Bits | Mode | Initial<br>Value | Name     | Description                                                                                |

|------|------|------------------|----------|--------------------------------------------------------------------------------------------|

| 7:1  |      |                  |          | Reserved                                                                                   |

| 0    | R    | 0                | OPSTATUS | Operation status<br>0 – operation finished, results are available<br>1 – operation running |

#### Address: 0x06

Register name: **RSTR**, ASIC software reset

| Bits | Mode | Initial<br>Value | Name | Description                                                                                                                                         |

|------|------|------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0  | W    | 0x00             | RSTR | ASIC software reset<br>0x00 – do not reset<br>0x01 – reset ASIC software (see section 2.8<br>for more details),<br>other combinations are reserved. |

#### Address: 0x07

Register name: STATUS, ASIC top-level status

| Bits | Mode | Initial<br>Value | Name           | Description                                                                                                                                          |

|------|------|------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7    |      |                  |                | Reserved                                                                                                                                             |

| 6    | R    | 0                | EXT<br>TRIGGED | Status due external trigger<br>0 – externally triggered acquisition is finished<br>1 – externally triggered acquisition is running                   |

| 5    | R    | 0                | DRDY           | Data ready (same behavior as DRDY-pin)<br>0 – no new results are available<br>1 – new results are available                                          |

| 4    | R    | 0                | RTERR          | Real time error<br>0 – no real time error<br>1 – real time error (interrupt has not been<br>serviced in time, cleared by DATARD16<br>read operation) |

| 3    | R    | 0                | OVP            | Over pressure bit<br>0 – normal pressure<br>1 – over pressure detected                                                                               |

| 2:1  |      |                  |                | Reserved                                                                                                                                             |

| 0    | R    | 0                | STARTUP        | Start-up status<br>0 – start-up procedure is finished<br>1 – start-up procedure is running                                                           |

# SPI address: 0x1F

TWI address: 0x7F

Register name: DATARD8, pressure data MSB or 8 bit data read from EEPROM

| Bits | Mode | Initial<br>Value | Name     | Description                     |

|------|------|------------------|----------|---------------------------------|

| 7:3  |      |                  |          | Reserved                        |

| 2:0  | R    | 000              | PRES_MSB | Pressure data MSB (3 bits)      |

| 7:0  | R    | 00h              | DATA     | 8 bit data from EEPROM register |

If EEPROM register is read the content of the DATARD8 register is the EEPROM register content. Otherwise pressure data MSB (bits [2:0]) can be read from DATARD8.

# SPI address: **0x20** TWI address: **0x80** Register name: **DATARD16**, pressure data LSB or 8 bit data read from indirect register

| Bits | Mode | Value | Name     | Description                       |

|------|------|-------|----------|-----------------------------------|

| 15:0 | R    | 0000h | PRES_LSB | Pressure data LSB (16 bits)       |

| 15:8 |      |       |          | Reserved                          |

| 7:0  | R    | 00h   | DATA     | 8 bit data from indirect register |

If indirect register is read the content of the DATARD16 register is the indirect register content (bits [7:0]). Otherwise pressure data LSB (bits [15:0]) can be read from DATARD16.

Bit level description for pressure data from registers DATARD8 and DATARD16 is presented in Table 12 below. Pressure information is presented in integer format. See section 2.2.3 (Equation 1) for more detailed information of converting the pressure data in to Pascal, [Pa].

Table 12. Bit level description of pressure data.

|               | DATARD8 |     |     | DATARD16 |      |      |      |     |     |     |    |    |    |    |    |    |    |     |      |

|---------------|---------|-----|-----|----------|------|------|------|-----|-----|-----|----|----|----|----|----|----|----|-----|------|

| Bit#          | B2      | B1  | B0  | B15      | B14  | B13  | B12  | B11 | B10 | B9  | B8 | B7 | B6 | B5 | B4 | B3 | B2 | B1  | B0   |

| ~[Pa]         | 64K     | 32K | 16K | 8192     | 4096 | 2048 | 1024 | 512 | 256 | 128 | 64 | 32 | 16 | 8  | 4  | 2  | 1  | 0.5 | 0.25 |

| Data<br>bit # | P18     | P17 | P16 | P15      | P14  | P13  | P12  | P11 | P10 | P9  | P8 | P7 | P6 | P5 | P4 | P3 | P2 | P1  | P0   |

# SPI address: 0x21 TWI address: 0x81

Register name: TEMPOUT, temperature in 2's complement format

| Bits  | Mode | Initial<br>Value | Name | Description             |

|-------|------|------------------|------|-------------------------|

| 15:14 |      |                  |      | Reserved                |

| 13:0  | R    | 0000h            | TEMP | Temperature output data |

Bit level description for temperature data from register TEMPOUT is presented in Table 13 below. See section 2.2.3 (Equation 2) for more detailed information of converting the temperature data in to [°C].

Table 13. Bit level description of1 temperature data.

|               |       | TEMPOUT |     |       |       |      |      |      |     |     |     |     |     |     |     |      |

|---------------|-------|---------|-----|-------|-------|------|------|------|-----|-----|-----|-----|-----|-----|-----|------|

| Bit#          | B15   | B14     | B13 | B12   | B11   | B10  | B9   | B8   | B7  | B6  | B5  | B4  | B3  | B2  | B1  | B0   |

| ~[°C]         |       |         | S   | 204.8 | 102.4 | 51.2 | 25.6 | 12.8 | 6.4 | 3.2 | 1.6 | 0.8 | 0.4 | 0.2 | 0.1 | 0.05 |

| Data<br>bit # | х     | x       | s   | T12   | T11   | T10  | Т9   | Т8   | Τ7  | Т6  | T5  | T4  | Т3  | T2  | T1  | Т0   |

| s = sia       | n bit |         |     |       |       |      |      |      |     |     |     |     |     |     |     |      |

x = not used bit

#### 3.3 Indirect Access Registers

SCP1000 indirect access register contents and bit definitions are described in this section. Indirect access registers can be accessed through the serial interface using the OPERATION, DATAWR, ADDPTR and DATARD16 registers (see section 3.3.1).

#### Address: 0x00

Register name: CFG, configuration register

| Bits | Mode | Initial<br>Value | Name | Description, INDIRECT ACCESS                                                                                                                                      |

|------|------|------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0  | RW   | 0x05             |      | Low power mode resolution selection:<br>0x05 – high resolution selected (17 bits)<br>0x0D – low resolution selected (15 bits)<br>other combinations are reserved. |

#### Address: 0x05

Register name: TWIADD, TWI device address

| Bits | Mode | Initial<br>Value | Name   | Description, INDIRECT ACCESS |

|------|------|------------------|--------|------------------------------|

| 7:0  | W    | 11h              | TWIADD | TWI device address           |

#### Address: 0x09

Register name: CFG2, MISO configuration, only for SPI devices

| Bits | Mode | Initial<br>Value | Name | Description, INDIRECT ACCESS                                                                                                                                           |

|------|------|------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0  | RW   | 13h              | CFG2 | MISO configuration:<br>0x13 – MISO in active drive mode<br>0x17 – MISO in open drain mode<br>other combinations are reserved.<br>Wait 100 ms after MISO is configured. |

See section 4.1.2 for further information of MISO configuration.

#### Address: 0x2D

Register name: **MODTEST2**, noise level configuration

| Bits | Mode | Initial<br>Value | Name     | Description, INDIRECT ACCESS                                                                                                                 |

|------|------|------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0  | W    |                  | MODTEST2 | Noise level configuration:<br>0x03 – reduced noise level<br>other combinations are reserved.<br>Wait 100 ms after noise level is configured. |

See section 2.1.2.2 for further information of noise level configuration.

#### 3.3.1 Example of indirect access register write and read operations

Example of indirect access register WRITE operation (write 0x0D to indirect register CFG, 0x00):

- Write 0x00 in direct register ADDPTR (0x02)

- Write 0x0D in direct register DATAWR (0x01)

- Write 0x02 in direct register OPERATION (0x03)

- o Wait 50 ms

Example of indirect access register READ operation (read indirect register 0x00):

- Write 0x00 in direct register ADDPTR (0x02)

- Write 0x01 in direct register OPERATION (0x03)

- o Wait 5 ms

- Read direct register DATARD16 (0x20 for SPI, 0x80 for TWI), bits [15:8] should be treated as zeros, the register content is in bits [7:0], see section 3.2 for further information.

#### 3.4 EEPROM memory

SCP1000 has internal non-volatile memory for calibration and configuration data. Memory content will be programmed during production. Initial configuration is loaded during sensor start-up.

EEPROM register contents and bit definitions are described in this section. User has access to 4 EEPROM registers. EEPROM registers can be accessed through the serial interface using the OPERATION, DATAWR, ADDPTR and DATARD8 registers (see sections 3.4.1 and 3.4.2).

Address: 0x29

Register name: USERDATA1, user accessible EEPROM register

| Bits | Mode | Initial<br>Value | Name      | Description                     |

|------|------|------------------|-----------|---------------------------------|

| 7:0  | RW   | 00h              | USERDATA1 | User accessible EEPROM register |

#### Address: **0x2A** Register name: **USERDATA2** user accessible FEPROM register

| regioter |      |                  |           |                                 |  |  |  |  |  |

|----------|------|------------------|-----------|---------------------------------|--|--|--|--|--|

| Bits     | Mode | Initial<br>Value | Name      | Description                     |  |  |  |  |  |

| 7:0      | RW   | 00h              | USERDATA2 | User accessible EEPROM register |  |  |  |  |  |

#### Address: 0x2B

Register name: **USERDATA3**, user accessible EEPROM register

| Bits | Mode | Initial<br>Value | Name      | Description                     |

|------|------|------------------|-----------|---------------------------------|

| 7:0  | RW   | 00h              | USERDATA3 | User accessible EEPROM register |

#### Address: 0x2C

Register name: USERDATA4, user accessible EEPROM register

| Bits | Mode | Initial<br>Value | Name      | Description                     |

|------|------|------------------|-----------|---------------------------------|

| 7:0  | RW   | 00h              | USERDATA4 | User accessible EEPROM register |

#### 3.4.1 EEPROM writing

Please note that in order to guarantee reliable EEPROM writing operation it is very critical to follow the requirements below. The minimum value for supply voltage at +25 °C temperature is 3.0 V during EEPROM register write operation. The peak current consumption is also significantly higher than in normal operation (~2 mA for 15 ms period per byte).

Example of WRITE operation to EEPROM register 0x29 (write 0xAA to EEPROM register 0x29):

- Write 0x29 in direct register ADDPTR (0x02)

- Write 0xAA in direct register DATAWR (0x01)

- Write 0x06 in direct register OPERATION (0x03)

- o Wait 50 ms

#### 3.4.2 EEPROM reading

The EEPROM can be read with nominal supply voltage, but the peak current consumption is significantly higher than in normal operation ( $\sim$ 1.5 mA for 20 µs period per byte).

Example of READ operation from EEPROM register 0x29 (read EEPROM register 0x29):

- Write 0x29 in direct register ADDPTR (0x02)

- Write 0x05 in direct register OPERATION (0x03)

- Wait 15 ms (minimum wait value)

- Read direct register DATARD8 (0x1F for SPI, 0x7F for TWI), the register content is in bits [7:0], see section 3.2 for further information.

#### 4 Serial Interfaces

Communication between SCP1000 sensor and master controller is based on serial data transfer and dedicated interrupt line (DRDY-pin). Depending on operation mode an external trigger pin (TRIG) can also be used in serial interfacing. Two different serial interfaces are available for SCP1000 sensor: SPI and TWI (very similar to I<sup>2</sup>C). However, only one interface per product is enabled by pre-programming in the factory. SCP1000 acts as a slave on both SPI and TWI bus.

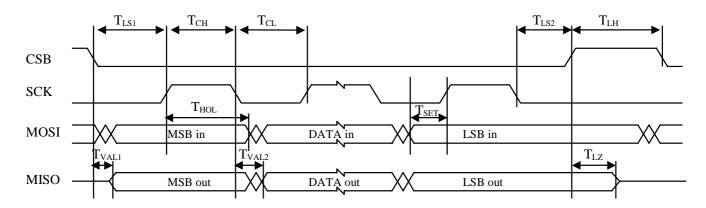

#### 4.1 SPI Interface

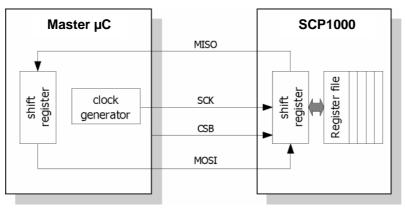

The SPI interface is a full duplex 4 wire serial interface. The connection between the  $\mu$ C and SCP1000 is done using MOSI, MISO, SCK and CSB. CSB selects the chip on multi-chip SPI bus, SCK is the serial data clock, MOSI is the data line from master to slave (Master Out Slave In) and MISO is data line from slave to master (Master In Slave Out). SCP1000 is configured to SPI slave mode (see Figure 8).

Figure 8. SPI master slave configuration.

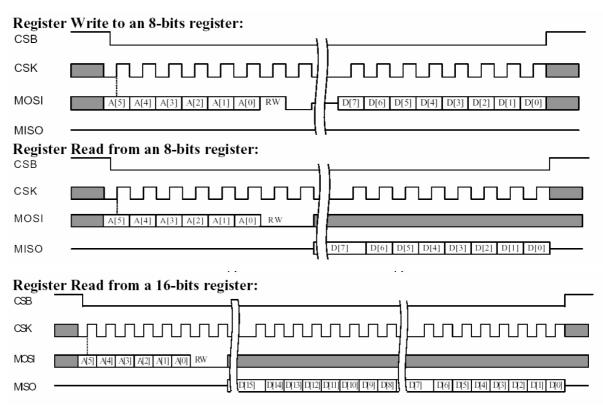

#### 4.1.1 SPI frame format

The SCP1000 SPI frame format is presented in Figure 9 below.

| CSB    | Γ                                                                                    |

|--------|--------------------------------------------------------------------------------------|

| sck_   |                                                                                      |

| MOSI_  | A5 X A4 X A3 X A2 X A1 X A0 X RBAW / D17 X D18 X D15 X D14 X D13 X D12 X D11 X D10 \ |

| MISO — | / D07 ( D08 ( D05 ( D04 ( D03 ( D02 ( D01 ( D00 )                                    |

Figure 9. SPI frame format for two 8 bit words.

Each SPI communication frame contains two or three 8 bit words: the first word defines the register address (6 bits wide, bits [A5:A0] in Figure 9) followed by the type of access ('0' = Read or '1' = Write) and one zero bit (bit 0, LSB). The following word(s) contain the data being read or written. The MSB of the words are sent first. Bits from MOSI line are sampled in on the rising edge of SCK and bits to MISO line are latched out on falling edge of SCK.

The CSB line must stay low during the entire frame accesses, i.e. between the bytes. If the CSB line state changes to high, the access is terminated. The CSB has to be pulled up after each communication frame. The word length (8 or 16 bits) is determined by the address value. If A[5] equals '1', the word length is 16 bits otherwise it is 8 bits.

#### 4.1.2 MISO line configuration

In SCP1000 the MISO line can be configured to operate either as

- o ACTIVE drive or

- o OPEN DRAIN drive.

By a default SCP1000 has been configured to operate as ACTIVE, thus it does not release the MISO line even if CSB is high. Operation mode can be reconfigured by changing the content of the CFG2 register.

SCP1000 MISO line has to be configured into open drain drive state, if other devices are connected to same SPI bus with SCP1000.

#### 4.1.2.1 MISO line configured to open drain drive state

If the SCP1000 MISO line is configured to operate in open drain mode an external pull up from MISO to DVDD is mandatory for the SPI operation (2 k $\Omega$  - 10 k $\Omega$  depending on SCK frequency, see Figure 10). In order to configure SCP1000 to operate with open drain MISO:

<u>Write 0x17 in indirect register 0x09</u> and wait for 100 ms. The actual write sequence in to indirect register is presented below:

- Write 0x09 in direct register 0x02 (ADDPTR)

- Write 0x17 in direct register 0x01 (DATAWR)

- Write 0x02 in direct register 0x03 (OPERATION "write indirect register")

- Wait for 100 ms

Figure 10. MISO line in open drain configuration.

When communicating with SCP1000 in SPI bus with other devices the direct access register REVID (0x00) has to be read always after the host has communicated with SCP1000, otherwise SCP1000 reserves the MISO line.

After power down mode, reset or start-up SCP1000 MISO has to be reconfigured again, otherwise the default value (MISO in active drive state) will be assigned to the register.

#### 4.1.2.2 MISO line configured to active drive state

In order configure SCP1000 to operate with active MISO (default setting after start-up):

<u>Write 0x13 in indirect register 0x09</u> and wait for 100 ms. The actual write sequence in to indirect register is presented below:

- Write 0x09 in direct register 0x02 (ADDPTR)

- Write 0x13 in direct register 0x01 (DATAWR)

- Write 0x02 in direct register 0x03 (OPERATION "write indirect register")

- o Wait for 100 ms

#### 4.1.3 Examples of SPI communication

Examples SPI communication (8 and 16 bit read / write operations) are presented in Figure 11 below.

Figure 11. SPI communication examples.

#### 4.2 TWI Interface

TWI is a 2-wire half-duplex serial interface. It consists of one master device and one or more slave devices. The master is defined as a micro controller providing the serial clock (SCL), and the slave as any integrated circuit receiving the SCL clock from the master. The SCP1000 sensor always operates as a slave device in master-slave operation mode. When in SPI interface a hardware addressing is used (slaves have dedicated CSB signals), the TWI interface uses a software based addressing (slave devices have dedicated bit patterns as addresses). Seven bit device addressing is used with SCP1000. The default TWI device address for SCP1000 is 0x11, b'001 0001' (pre-programmed during SCP1000 production).

The two wires in TWI bus are:

- o SCL, serial clock and

- SDA, bi-directional data line.

The SCL pin of SCP1000 is an input pin (SCP1000 never controls the SCL line). Data is transferred in and out of the sensor through the bi-directional SDA pin. SDA has an open-drain output, so an external pull-up resistor to DVDD is required (see Figure 12). The minimum value for SDA pull-up resistor is 2 k $\Omega$ .

Figure 12. TWI master slave configuration.

External pull-up resistor from SCL to DVDD is not needed if master drives SCL actively to high and low states. There is no de-bouncing is implemented in the SCP1000 digital I/O pads, so the signals on SDA and SCL must be clean.

#### 4.2.1 TWI frame format

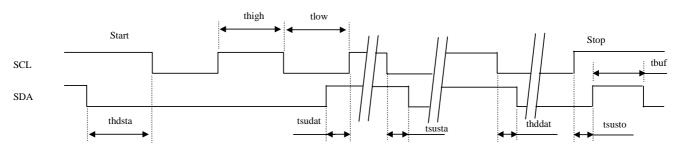

TWI transactions are based on a byte-long transfers separated by acknowledgements. Bits from SDA line are sampled in on the rising edge of SCL and bits to SDA line are latched out on falling edge of SCL. Master starts and stops the communication by sending start and stop bits. After start bit master sends device TWI device address. The communication continues with predefined frame format. General patterns of TWI frame format are described below.

#### START BIT ( $\mu C \rightarrow SCP1000$ )

The start bit is a high to low transition on SDA, while SCL is high. When the master issues a start bit, it takes the control of the bus.

#### SLAVE DEVICE ADDRESS ( $\mu C \rightarrow SCP1000$ )

Master sends a 7 bit slave device address, bits [7:1], MSB first. SCP1000 device address is 0x11, b'001 0001' by default. The LSB (bit 0) indicates the type of access ('0' = Read or '1' = Write).

#### ACKNOWLEDGE BIT

The transmitter of the acknowledge bit must tie the SDA line to low to perform an acknowledgement. The receiver of the acknowledge bit must release the SDA line because at this time, it is not the master of the TWI bus. The receiver then checks the acknowledge bit by reading a '0' on SDA.

#### REGISTER ADDRESS ( $\mu C \rightarrow SCP1000$ )

Master sends register address to SCP1000 MSB first.

#### REGISTER DATA (SCP1000 $\rightarrow \mu$ C)

The SCP1000 registers can be 8 or 16 bits wide. An 8 bit write is performed by sending MSB first. A 16 bits write is performed by sending two bytes (MSB first). After each byte, the slave sends an acknowledgement bit.

#### STOP BIT ( $\mu C \rightarrow SCP1000$ )

The stop bit is a low to high transition on SDA, while SCL is high. The master, who has generated the stop bit, sets the bus free.

#### REPEATED START ( $\mu C \rightarrow SCP1000$ )

A repeated start is a start signal generated by a master, which has already taken the control of the TWI bus. It is used by the master to initiate a transfer with a new slave, or with the same slave, in the other communication mode (transmit or receive mode), without releasing the bus.

#### NOT ACKNOWLEGDE BIT:

If the receiver of the acknowledge bit reads a '1' on SDA line during an acknowledge clock pulse, that means transmitter did not acknowledge. The master uses the not acknowledge bit to terminate a read action.

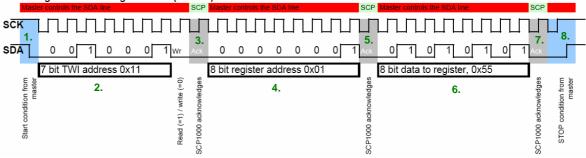

#### 4.2.1.1 TWI write sequence

8 bit TWI write sequence is presented in Figure 14 and described below:

- 1. **START BIT** (to initiate a transmission, the master sends a start bit)

- 2. SLAVE DEVICE ADDRESS (slave device address with WRITE access  $\rightarrow$  LSB = '0')

- 3. SLAVE ACKNOWLEDGEMENT (having identified device address as its own, slave acknowledges by sending an acknowledge bit)

- 4. **REGISTER ADDRESS** (the 8 bit address of the register to be written, MSB first)

- 5. **SLAVE ACKNOWLEDGEMENT** (the slave sends an acknowledgement bit)

- 6. **REGISTER DATA** (master sends the data to be written to the addressed register)

- 7. **SLAVE ACKNOWLEDGEMENT** (after receiving the byte, the slave sends an acknowledgement bit)

- 8. STOP BIT (master sets the bus free)

8 bit register write in register 0x01 (DataWr)

Figure 14. TWI frame format for 8 bit write operation (numbers from 1 to 8 refer to list above).

#### 4.2.1.2 8 bit TWI read sequence

8 bit TWI read sequence is presented in Figure 15 and described below:

- 9. **START BIT** (to initiate a transmission, the master sends a start bit)

- 10. SLAVE DEVICE ADDRESS (slave device address with WRITE access  $\rightarrow$  LSB = '0')

- 11. SLAVE ACKNOWLEDGEMENT (having identified device address as its own, slave acknowledges by sending an acknowledge bit)

- 12. REGISTER ADDRESS (the 8 bit address of the register to be read, MSB first)

- 13. SLAVE ACKNOWLEDGEMENT (the slave sends an acknowledgement bit)

- 14. REPEATED START (from master)

- 15. SLAVE DEVICE ADDRESS (slave device address with READ access  $\rightarrow$  LSB = '1')

- 16. **SLAVE ACKNOWLEDGEMENT** (the slave acknowledges)

- 17. **REGISTER DATA** (the master continues sending the SCK pulses as slave sends the defined register content to SDA line)

- 18. **MASTER NOT ACKNOWLEDGE** (master terminates the data transfer by sending not acknowledge bit)

- 19. STOP BIT (master sets the bus free)

8 bit read from register 0x7F (DataRd8), bits [2:0] are used for pressure information SCK 16 13 11. SDA 0 0 1 0 0 0 1 Wr 0 1 0 0 1 1 R 0 7 bit TWI bit TW 8 bit r from Î î rom 15. 12. 17. 10. write ( does write ( anknowla Master (II) ackn (=1)/ ack Start estart SCP1000 SCP1000 CP1000 Read Read

Figure 15. TWI frame format for 8 bit read operation (numbers from 9 to 19 refer to list

#### 4.2.1.3 16 bit TWI read sequence

16 bit TWI read sequence is presented in Figure 16 and described below:

- 20. **START BIT** (to initiate a transmission, the master sends a start bit)

- 21. SLAVE DEVICE ADDRESS (slave device address with WRITE access  $\rightarrow$  LSB = '0')

- 22. SLAVE ACKNOWLEDGEMENT (having identified device address as its own, slave acknowledges by sending an acknowledge bit)

- 23. **REGISTER ADDRESS** (the 8 bit address of the register to be read, MSB first)

- 24. SLAVE ACKNOWLEDGEMENT (the slave sends an acknowledgement bit)

- 25. REPEATED START (from master)

- 26. SLAVE DEVICE ADDRESS (slave device address with READ access  $\rightarrow$  LSB = '1')

- 27. SLAVE ACKNOWLEDGEMENT (the slave acknowledges)

- 28. **MSB BYTE OF REGISTER DATA** (the master continues sending the SCK pulses as slave sends the defined register MSB content to SDA line)

- 29. **MASTER ACKNOWLEDGEMENT** (the master acknowledges after it has received the first 8 bit byte of register content)

- 30. LSB BYTE OF REGISTER DATA (the master continues sending the SCK pulses as slave sends the defined register LSB content to SDA line)

- 31. **MASTER NOT ACKNOWLEDGE** (master terminates the data transfer by sending not acknowledge bit)

- 32. **STOP BIT** (master sets the bus free)

16 bit read from register 0x80 (DataRd16), bits [15:0] are used for pressure information

Figure 16. TWI frame format for 16 bit read operation (numbers from 20 to 32 refer to list above).

#### **5** Electrical Characteristics

#### 5.1 Absolute Maximum Ratings

The absolute maximum ratings of SCP1000 are presented in Table 14 below.

Table 14. Absolute maximum ratings of SCP1000.

| Parameter                                   | Value                           | Unit |

|---------------------------------------------|---------------------------------|------|

| Supply voltage (V <sub>dd</sub> )           | -0.3 to +3.6                    | V    |

| Voltage at input / output pins <sup>1</sup> | -0.3 to (V <sub>dd</sub> + 0.3) | V    |

| ESD (Human body model)                      | ±2.0                            | kV   |

| Storage temperature                         | -30 +85                         | °C   |

| Proof pressure                              | 2.0                             | MPa  |

| Ultrasonic cleaning                         | Not allowed                     | l    |

| <sup>1</sup> Referred to DVDD               |                                 |      |

#### 5.2 Power Supply

The analog and digital supply voltage levels (AVDD and DVDD) should always be equal.

#### 5.3 Digital I/O Specification

#### 5.3.1 Digital I/O characteristics

SCP1000 has no pull-up/down resistors in any pins.

Table 15. Characteristics of digital I/O pins.

|                                     | Parameter                                       | Conditions                | Symbol             | Min      | Тур | Max      | Unit |

|-------------------------------------|-------------------------------------------------|---------------------------|--------------------|----------|-----|----------|------|

| Input: CSB, MOSI, SCK/SCL, TRIG, PD |                                                 |                           |                    |          |     |          |      |

| 1                                   | Input high voltage                              |                           | V <sub>IH</sub>    | 0.7*DVDD |     |          | V    |

| 2                                   | Input low voltage                               |                           | V <sub>IL</sub>    |          |     | 0.3*DVDD | V    |

| 3                                   | Hysteresis                                      |                           | $V_{HYST}$         | 0.1*DVDD |     |          | V    |

| 4                                   | Absolute maximum value<br>of input peak current |                           | I <sub>in</sub>    |          |     | 1        | μA   |

| 5                                   | Input capacitance                               |                           | C <sub>in</sub>    |          | 1.6 |          | pF   |

| 6                                   | TRIG pulse width                                | Figure 17                 | T <sub>wtrig</sub> | 200      |     |          | ns   |

| Outp                                | ut terminal: MISO/SDA, DRD                      | Y                         |                    |          |     |          |      |

| 7                                   | Output high voltage                             | I <sub>out</sub>   = 1 mA | V <sub>OH</sub>    | 0.8*DVDD |     | DVDD     | V    |

| 8                                   | Output low voltage                              | I <sub>out</sub>   = 1 mA | V <sub>OL</sub>    | 0        |     | 0.2*DVDD | V    |

| 9                                   | Absolute value of output current                |                           | I <sub>out</sub>   |          |     | 1        | mA   |

| 10                                  | Load capacitance                                |                           | Cout               |          |     | 50       | pF   |

Figure 17. TRIG pulse timing.

#### 5.3.2 SPI AC characteristics